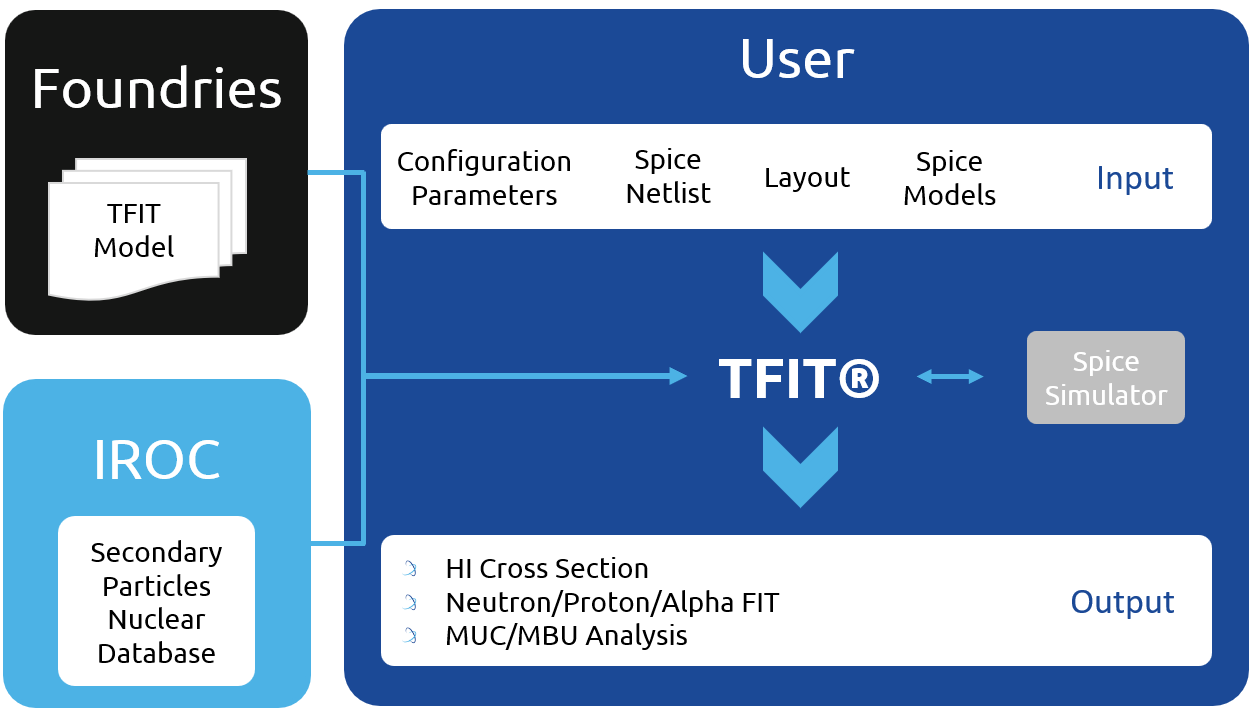

TFIT® (Transistor Failure In Time) is a best-in-class transistor/cell level soft error simulator. Thanks to its unique approach and close collaboration with foundries, TFIT enables high-speed, accurate simulation of the radiation effects of standard cells and custom designs implemented in main process nodes available on the market.

The TFIT methodology is based on foundry provided characterization models of ionizing particles for each technology node. TFIT innovative algorithms lean on these foundry models to simulate radiation effects accurately at the spice level up to 100X faster than TCAD based solutions.

TFIT makes it easy to:

- Find the raw cross-sections/FIT values of the basic cell used in the circuit

- Understand and improve the sensitivity of cell design

- Find the optimal area for radiation hardened design

- Find the smallest SRAM configuration without Multi Bit Upset

The TFIT models offer the basics for handling soft error rate calculations for the following environments:

- Heavy ions

- High energy neutrons

- Protons

- Alpha particles

- Thermal neutrons

IROC is partnering with major foundries and offers many foundry approved TFIT models from main stream process nodes are available.

Foundry

Available TFIT Models

TSMC

65G, 40G, 28HP, 16FF, N10, N7, N5, N3

SAMSUNG

32nm, 28nm, 14nm, 10nm, 7nm

GlobalFoundries

40G, 40Fab1, 28SLP, 22FDX

STM

65nm, 28FDX

In addition to the target technology, TFIT

requires the Spice netlist and the GDS files of the analyzed design. TFIT

detects the various logical states of the input design and performs the requested

analysis on each of these states.

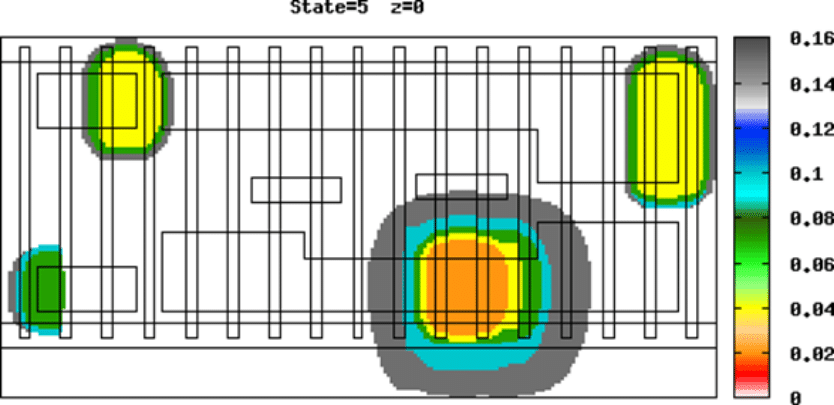

In addition to a log file containing Soft Error Rate (SER) details, TFIT outputs the sensitivity maps showing sensitive zones of the design as a function of Linear Energy Transfer. This can be helpful for understanding and optimizing sensitivity.

TFIT offers rich features covering a wide variety of applications requiring good or high levels of reliability. This is detailed in the table on the right:

- Heavy Ions Cross Section Computation (space application)

- High Energy Neutron FIT Computation (ground level application)

- Proton FIT Computation (space application)

- Alpha Particle Cross Section and FIT value Computation

TFIT

Ground application

Space application

Specific application

- Neutron SET/SEU FIT Value

- Heavy ion cross-sections for SET/SEU

- Thermal neutron FIT value

- SRAM MCU/MBU FIT and pattern

- Proton cross-section for SET/SEU

-

Alpha particle SET/SEU

FIT value

Access to a standard spice simulator supporting simulation technology is mandatory to use TFIT. The following commercial simulators are supported:

- Hspice and Finesim (Synopsys)

- Spectre (Cadence)

- Eldo (Siemens EDA)

Other Spice simulators could be supported upon request.

Simulation type

Performance

Single particle impact

Few seconds

Cross Section

Few minutes

LET threshold

< 1 minute

SEU Neutron FIT

~ 5 minutes

Alpha FIT

MCU/MBU

~ 5 minutes

~ 30 minutes

TFIT - best-in-class cell level soft error detector

TFIT - best-in-class cell level soft error detector - IROC

TFIT - best-in-class cell level Soft Error detector, TFIT - best-in-class transistor level Soft Error detector - IROC TECHNOLOGIES