SoCFIT is a state-of-the-art EDA tool for reliability-focused design characterization of complex digital circuits. It enables digital designers to understand the propagation of faults in the circuit and their impact on the system. This allows them to assess the compliance of their solutions with set reliability targets and functional safety standards. With SoCFIT, designers can significantly reduce reliability constraints and minimize the cost of mitigating faults in terms of design effort, silicon area and power consumption.

SoCFIT is a complete SER analysis platform, which provides a comprehensive set of algorithms and solutions, applicable from circuit- to system-level. Depending on the design stage and the reliability expectations of the application, the trade-off between accuracy and effort can be adjusted to meet quality requirements without excessive costs from over-design.

In the context of functional safety analysis (such as ISO26262 for automotive applications), SoCFIT is able to estimate the number of safe faults that are not considered in the analysis.

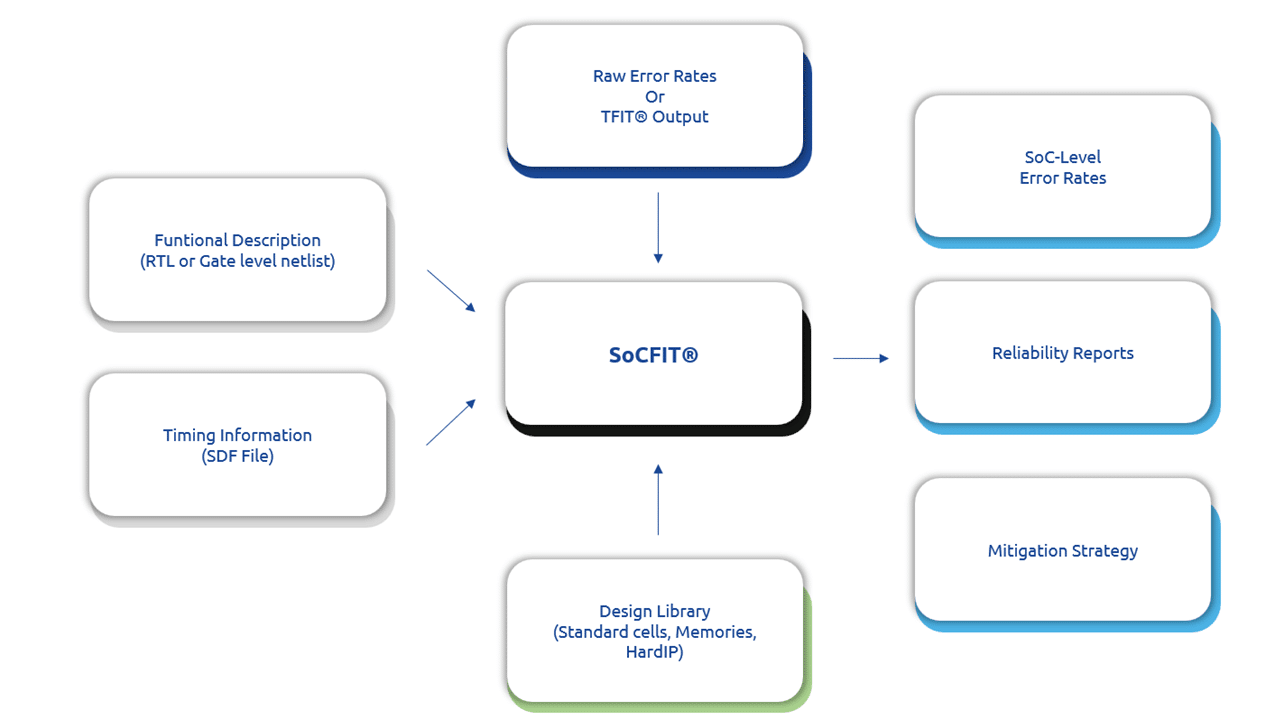

SoCFIT’s analysis is based on the functional description of the digital circuits and the raw failure rates of basic design elements.

The functional description of the circuit consists of its HDL description. SoCFIT can read Verilog and VHDL designs (System Verilog on request). SoCFIT analysis can be performed on RTL or Gate level netlist descriptions.

To estimate SoC level failure rate, SoCFIT starts with the raw error rate of each design elements (standard cells, memories, hard IP, …). This information provides the intrinsic error rate of the technology for a given environment and can be obtained in several ways:

- From the foundry, IP provider, or cell designers

- By performing radiation tests on elementary test structures

- By running simulation based approaches with e.g. TFIT

Based on this input, SoCFIT provides error rates for each module up to the SoC level. From the early phases of design, SoCFIT generates reliability reports and help to define SER mitigation strategies that minimizing design cost.

In the later stages of design, the accuracy of the analysis can be increased by considering actual technology and timing information. SoCFIT is also able to read the description of standard cell libraries, typically in Verilog format in order to analyze the synthesized or placed and routed design. SoCFIT can use the timing information of the design, provided as SDF files generated by standard timing analysis tools, to evaluate the temporal masking of faults.

SoCFIT implements a large set of algorithms to model the propagation of faults, ensuring thorough understanding of the impact of faults on both the circuit and application level. Users can select the most appropriate approach to perform their reliability analysis depending on the design stage and their failure rate requirements. The purpose of each of these algorithm is to compute a derating factor, which represents the proportion of faults that can propagate through the system.

SoCFIT provides algorithms and support for the following masking mechanisms:

Sequential Logic

Combinational Logic

Memory

- Logicial Masking

- Temporal Masking

- Functional Masking

SoCFIT - unique SoC level soft error analysis and mitigation

SoCFIT - unique SoC level soft error analysis and mitigation

SoCFIT - unique SoC level Soft Error analysis and mitigation, system level Soft Error analysis and mitigation - IROC TECHNOLOGIES